Risc V Instruction Set Cheat Sheet

Risc V Instruction Set Cheat Sheet - A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits. Similarly, auipc then jalr can. 16 integer registers instead of 32.

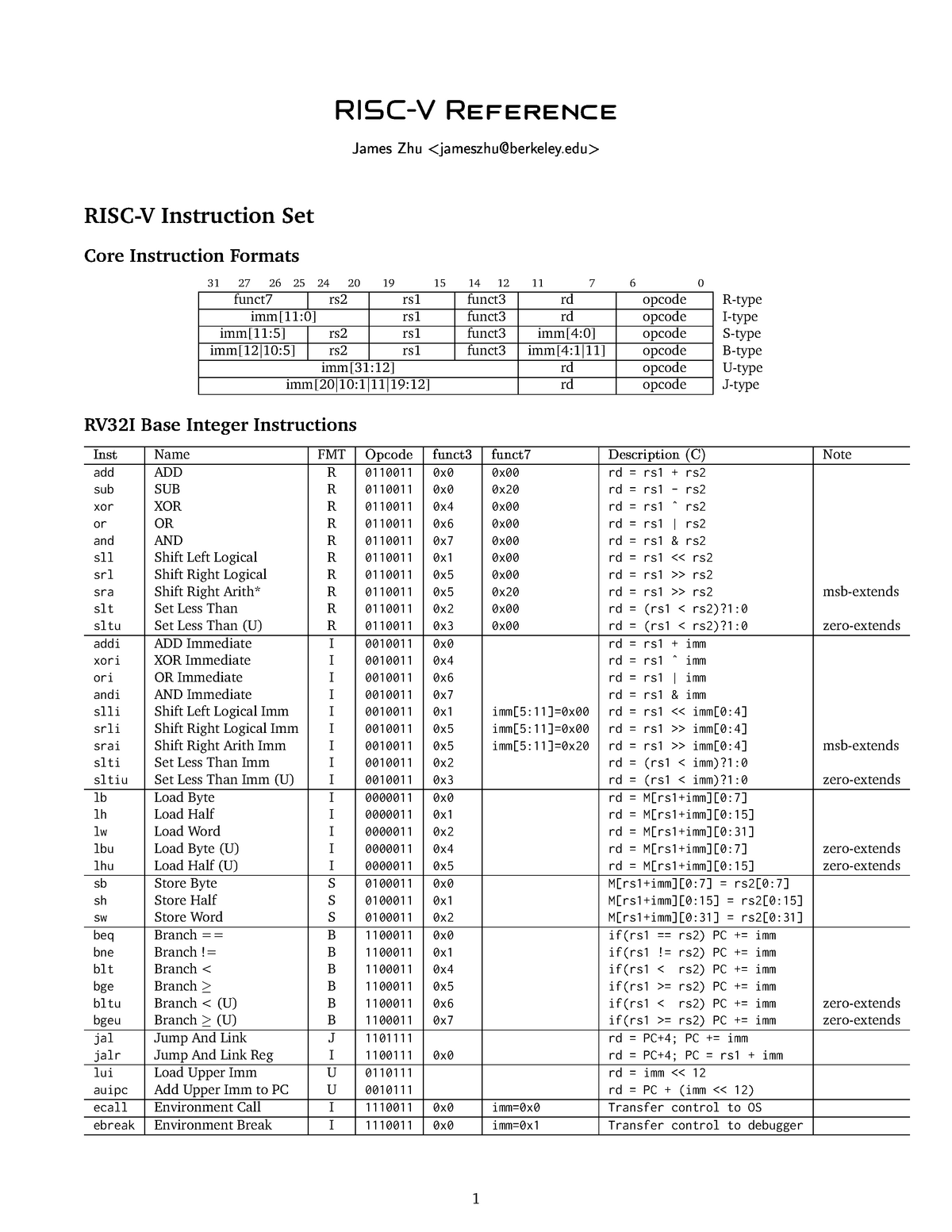

A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits. Similarly, auipc then jalr can. 16 integer registers instead of 32.

16 integer registers instead of 32. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits. Similarly, auipc then jalr can.

RISCV InstructionSet Cheatsheet By Erik Engheim ITNEXT, 50 OFF

Similarly, auipc then jalr can. 16 integer registers instead of 32. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits.

RISCV InstructionSet Cheatsheet by Erik Engheim ITNEXT

A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits. Similarly, auipc then jalr can. 16 integer registers instead of 32.

Riscvcard riscv instructions list RISCV Reference ♠ s ♠ s③ r ②

16 integer registers instead of 32. Similarly, auipc then jalr can. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits.

Instruction set of the proposed XPosit RISCV extension. Download

Similarly, auipc then jalr can. 16 integer registers instead of 32. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits.

PDF] The RISCV Instruction Set Manual Semantic Scholar, 40 OFF

Similarly, auipc then jalr can. 16 integer registers instead of 32. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits.

RISCV InstructionSet Cheatsheet By Erik Engheim ITNEXT, 50 OFF

Similarly, auipc then jalr can. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits. 16 integer registers instead of 32.

Table 1.2 from The RISCV Instruction Set Manual Semantic Scholar

16 integer registers instead of 32. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits. Similarly, auipc then jalr can.

RISCV InstructionSet Cheatsheet by Erik Engheim ITNEXT

Similarly, auipc then jalr can. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits. 16 integer registers instead of 32.

RISCV InstructionSet Cheatsheet r/RISCV

16 integer registers instead of 32. Similarly, auipc then jalr can. A lui instruction can first load rs1 with the upper 20 bits of a target address, then jalr can add in the lower bits.

A Lui Instruction Can First Load Rs1 With The Upper 20 Bits Of A Target Address, Then Jalr Can Add In The Lower Bits.

Similarly, auipc then jalr can. 16 integer registers instead of 32.

![PDF] The RISCV Instruction Set Manual Semantic Scholar, 40 OFF](https://d3i71xaburhd42.cloudfront.net/ba52210f8b259a6057132251d03fb96c2dd66b6c/22-Table2.5-1.png)